021-80120081

021-80120081免费服务热线

Sigrity Aurora-融合Allegro用户体验与Sigrity强大功能

本文翻译自Cadence “Breakfast Bytes Blogs”专栏作者Paul McLellan文章 “Sigrity Aurora: In-Design Analysis“。

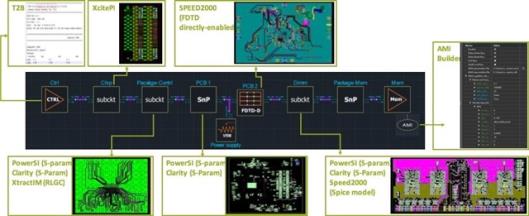

Cadence最新发布的SigrityTM Aurora工具将Allegro®用户体验与Sigrity引擎的强大功能相结合。借助这项新工具,设计团队能够在Allegro单一环境中实现:初步探索、设计、仿真分析、最终验证和签发的完整设计流程。这意味着,设计团队无需再在两个不同的设计软件环境中复制、粘贴设计,即可轻松获取设计数据。

在90年代Cadence收购Sigrity之前,Allegro软件中便已经具有信号完整性分析引擎。但是,正如手表定律(Segal’s Law)所言:“拥有一块手表可以知道时间;而拥有两块手表,反而无法确定时间。”同理,同时拥有一个集成到工具中的信号完整性引擎与另一个独立用于签发的信号完整性引擎亦会引发混乱:因为当两者显示的电压不一致时,无法确定何者正确。现在,Allegro集成最先进的信号与电源完整性分析引擎,为用户提供设计同步分析(In-Design Analysis, IDA)。

探索

在设计的早期阶段,我们可以通过What-if假设分析来确保计划成功。我们可以执行包括:阻抗和耦合检查、返回路径检查、反射和串扰分析、压降分析在内的信号完整性和电源完整性分析;并通过新的拓扑结构探索器进行布线前提取和信号网络提取。这些分析基于原理图而进行。此外,我们也可以将噪声注入到电源,而不是使用“理想”电源进行分析。

系统中的每个区块模型都能够采用Sigrity或Clarity技术构建。如此一来,实现对整个路径进行端到端分析——例如,上图所示:从芯片到电路板、再通过连接器到电缆、再到另一个连接器、另一个电路板,最终到达接收器。

(有关Clarity的更多信息,请访问Clarity产品页面;有关Sigrity的更多功能详情,请参见“版本升级: Sigrity 2019、Allegro/OrCAD 17.4现已发布”一文。)

设计

复杂的信号完整性规则检查可以在设计中运行,而无需设计人员深谙信号完整性知识。可执行的检查包括:

· 阻抗分析筛查:这项检查针对阻抗异常,例如,可检测出穿过下层接地层中缝隙的信号。这不一定是错误,但设计人员需要对此了解。

· 耦合分析筛查:由于两个信号在较长线路上近距离运行,可能会出现过度耦合,而这种情况也可能出现在电路板中不同的两层上。

· 返回路径筛查:针对可能出现返回路径问题网络提出报告,能够提供返回路径的品质因数。设计人员还能识别电路板上的返回电流。

验证

信号完整性工程师能够使用行业标准的IBIS模型进行设计同步反射和串扰分析。(有关IBIS的更多信息,请参见“DesignCon:Cadence与IBM联手讲授高级IBIS-AMI技术“一文)

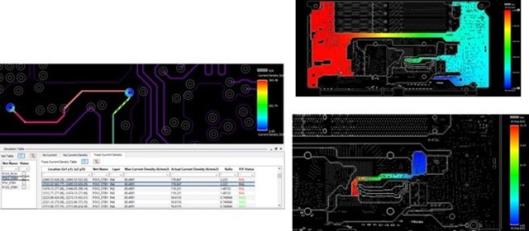

同时也能进行压降分析并在layout上显示为电压、压降、或电流密度(如下图所示):

Allegro PCB Symphony功能让团队成员能够在同一电路板上同时进行并行设计。现在,这一功能同样支持设计同步信号完整性和电源完整性分析, 而无需像过去一样对设计进行复制。

设计同步分析

Sigrity Aurora使设计人员能够在设计的各个阶段进行设计同步分析,从早期基于原理图的设计前分析、到设计过程中的电气规则检查分析、再到详细的布线后签发分析。这反映了Cadence的工具理念,即力求在各个设计阶段——从设计到签发,均使用同一引擎,以提高设计效率。

如欲了解更多内容,欢迎访问Cadence产品页面。

摘自Cadence官方博客