021-80120081

021-80120081免费服务热线

我们于去年正式发布了 Integrity 3D-IC 平台,为基于多晶粒的 3D 芯片设计提供了全新的自动化解决方案。利用多晶粒实现高性能系统集成的趋势持续已久。

Integrity 3D-IC 平台具有如下特性:

❖集成式 3D 设计规划和设计实现

❖早期热、功耗和静态时序分析功能

❖系统驱动的晶粒(Chiplet)功耗、性能和面积目标(PPA)优化

为什么选择多晶粒设计?

针对为什么要选择基于多晶粒(有时也被称作堆片)的设计方案,一篇完整的论文也说不完。

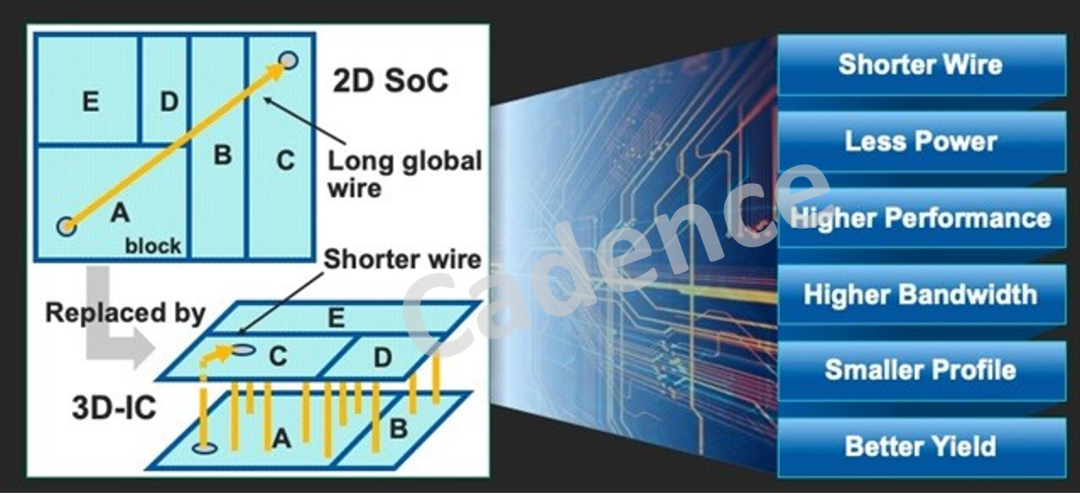

基于晶粒的设计可以规避单片集成的如下局限性:

当测试芯片的功能性和表征化在上一代工艺已经通过验证的情况下,几乎没人愿意把测试芯片用于设计关键路径最先进的 SerDes(比如 112G)上。

解决上述问题的方法就是 3D 堆叠。近些年,设计团队一直在采用这一方法,只不过还是会单独设计每个晶粒,然后将其集成成为一个完整系统,这一过程的自动化水平以往并不高。Integrity 3D-IC 平台将自动化带到了这一领域。

Integrity 3D-IC 平台

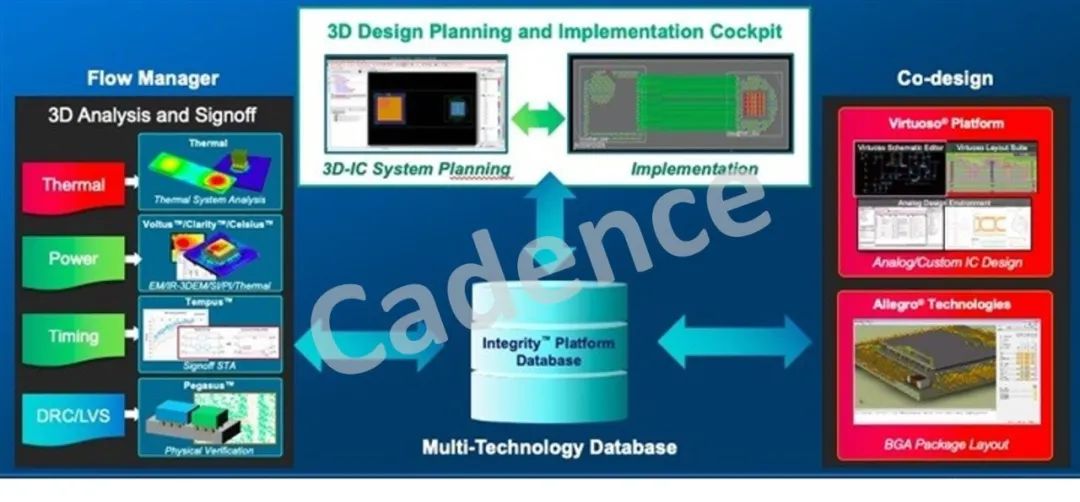

Cadence Integrity 3D-IC 平台是面向异构和同构 2.5D 及 3D 多晶粒堆叠式设计的设计规划、物理实现和系统分析统一集成的综合解决方案。平台由多个模块式子流程组成,包括支持物理设计实现及早期分析的系统级规划和分析工具,让 3D-IC 设计获得更高的生产效率。

上图展示了 Integrity 3D-IC 的架构。位于中间的是全新的 Integrity 平台数据库。数据库采纳了多项技术,设计流程中的每个晶粒都可以单独配置不同的工艺节点和 PDK。

左边是分析工具,都已获得更新且支持基于晶粒的设计流程。尤其是升级后的 Tempus 时序签核解决方案现已具备快速自动化芯片间分析功能,可以减少签核角组合数量,进而大幅缩短静态时序分析的时间。Tempus ECO 也获得了拓展,可以支持多晶粒系统中的设计改动。每个堆叠在一起的晶粒都是一个隔热层,所以 Celsius 的热分析对多晶粒设计也很关键,并确保任何来自不同晶粒上的热区不会相互重叠。

最上方是深度集成 Innovus™ 设计实现系统的版图规划和设计实现,与 3D-IC 系统规划一起可以实现更复杂的系统级设计规划。

右边则是模拟、定制化设计芯片和封装,其实现通过与 Cadence 其它工具的协同设计完成。包括:

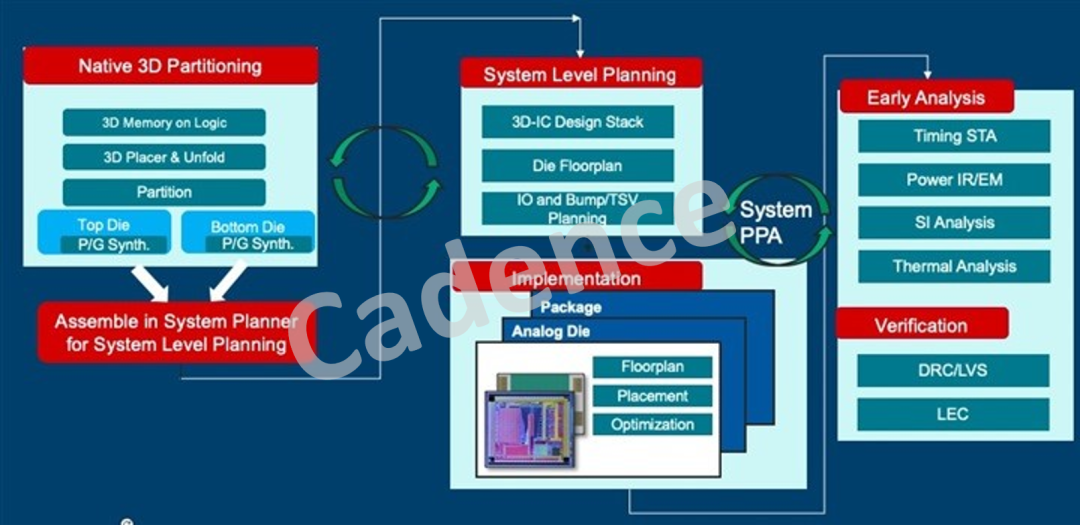

Integrity 3D-IC 是业界首款支持系统驱动 PPA 的集成式平台。PPA 指的是性能、功耗和面积。实际上,更准确地说,面积应该指的是成本。因为除了多晶粒的面积以外,设计流程中还有其他的成本。但 PPA 毕竟已经用了这么久,很难再去改变它的说法。

在一些多晶粒设计中,晶粒的定义需要预先规划;也有一些情况下,可以通过将 2D 设计拆分至 3D 设计来实现标准设计的功耗、性能和面积(PPA)优化。一个方法是人工判断各逻辑分区应该位于顶层芯片还是底层芯片,建立起 3D 堆叠的设计逻辑。另一个方法正在获得更多关注和应用,即把宏单元放在一颗晶粒上,把标准单元放在另一颗晶粒上。有一个特殊场景,当所有的宏单元都是内存时,你最后会得到一个逻辑晶粒和一个内存晶粒。将内存晶粒搭在逻辑晶粒上可以显著降低内存延迟。当然了,分区无法做到如此彻底,因为内存的测试逻辑最好还是搭载至内存晶粒上。

多晶粒堆叠的设计方法在 Integrity 面世前就已经存在,比如 Arm Neoverse N1 的设计实现就采用了这一分区方式。但随着 Integrity 3D-IC 平台的发布,这一设计可以更便捷的在支持多晶粒设计的平台数据库上通过 Innovus 完成设计实现并通过 Cadence 的签核工具完成后续签核。

(文章来源公众号: Cadence楷登PCB及封装资源中心)