021-80120081

021-80120081免费服务热线

本文翻译转载于 Cadence blog

作者 Vinod Khera

移动数据的迅速攀升,蓬勃发展的人工智能及机器学习(AI / ML)应用,和 5G 通信对带宽前所未有的需求对现有云数据中心的服务器、存储和网络架构形成了巨大压力。这些颇具挑战性的应用需要高 I / O 带宽和低延迟通信的支持。

由于超大规模数据中心需要 12.8Tbps 甚至更高的网络交换带宽,ASICs 和 SoC 对 112G SerDes IP 的需求也应运而生。Cadence 的 112G SerDes 技术具有卓越的长距性能、优秀的设计裕度、优化的功耗和面积,是下一代云网络、AI / ML 和 5G 无线应用的理想选择。

SerDes PHY IP 支持 PAM4 和 NRZ 信号调制,以及从 1G 到 112G 的数据传输速率,采用业界领先的模拟-数字转换器(ADC),时钟数据恢复(CDR)和数字信号处理(DSP)技术,可支持 40dB 以上的通道。该技术可实现背板、直连电缆(DAC)、芯片到芯片、以及芯片到模组间的高速数据传输,实现高性能计算(HPC)SoC。采用了 7nm 制程工艺的 Cadence® 112Gbps 多速率 PAM4 SerDes IP 助力达成业界领先的功耗、性能和面积(PPA)目标,面向下一代云端架构和电信数据中心打造高端口密度的网络产品。

高速 SerDes 的市场趋势

56G / 112G SerDes IP 属于高速 I / O,支持超大规模计算客户所需的指数级流量增长,推动制定采用 8 条 112G 链路的 800G 标准。业界龙头企业已发布了 25.6TB 交换机产品,下一代 51.2TB 产品也即将推出。这些高带宽交换机会使用ASICs,并将 112G PAM4 SerDes 作为基础 IP。支持 51.2TB 交换机的吞吐量需要大量的 I / O,但将其整合至同一个 SoC 则是一大挑战,在封装设计和功耗管理方面都需要作出突破。

在即将推出的协同封装硅片(CPO)解决方案中,裸片和光学多晶粒被集成到同一个封装中,以此避免在 PCB 板上的长距离布线,并拥有更高的吞吐量。得益于支持多插槽配置和芯片间互联的高速 I / O 接口,高带宽以及低延迟,112G SerDes 的另一个应用场景是 AI / ML SoC。5G 应用同样需要高带宽,112G SerDes 也是理想的选择。

挑战

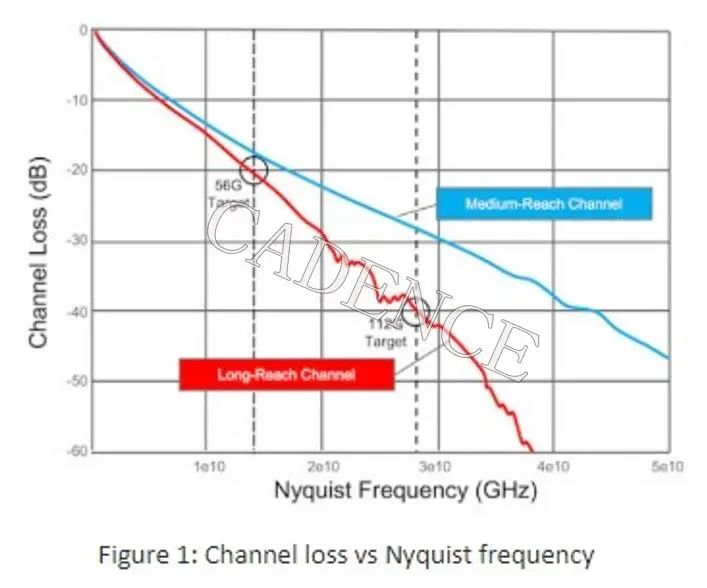

112G SerDes 技术可以满足数据密集型应用对高速互联的需求。但是,长距离连接需要更先进的服务器和网络设备,其设计本身就是巨大的挑战。由于奈奎斯特频率的翻倍,112G 系统的通道损失远超过 56G 系统,解决这一问题需要新的 SerDes 设计方法,如图一所示。

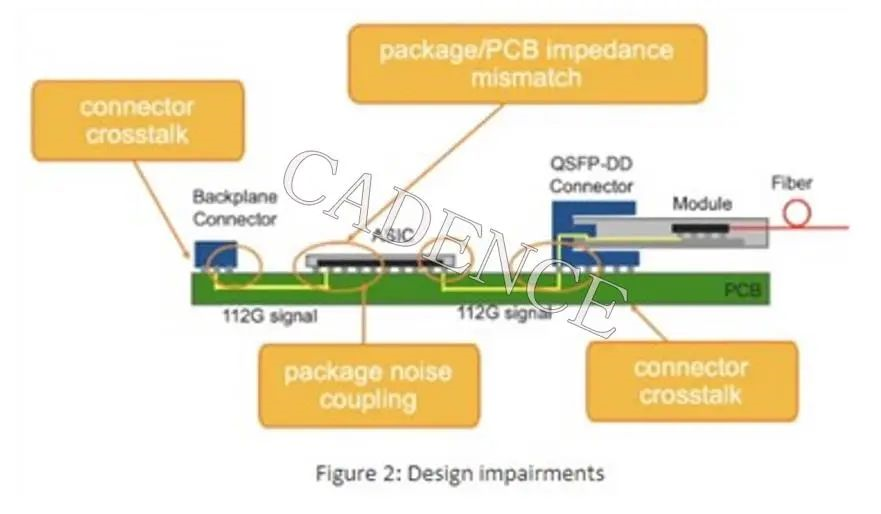

由于系统中的设计缺陷,112G 的部署也面临挑战,如图二所示。SoC 封装,封装到母板阻抗失配,前面板和背板的串扰以及噪声耦合等设计问题均会对误码率(BER)产生显著影响。由于更小的 UI 和更低的 SNR,我们在采用 112G 数据速率的过程中还会遇到更大的挑战。

因此,在设计阶段就确保总体通道性能满足 IEEE 标准至关重要。通道性能不应仅依据插入损耗判断。IEEE 标准指出,应将通道运行裕度(COM)作为测量标准。通过预先规定 COM 的最小值,这一标准允许设计师在满足 BER 规范的前提下自行选择优化信号缺陷和均衡方案。在包括 RX / TX 规范、串扰、抖动、码间干扰(ISI)和噪声等多维设计空间中,优秀的设计应该考虑 COM 的最大值。COM 的目的是用最少的指定 SerDes 对系统中的通道进行表征化,但是 COM 也可以检查高速串行系统的互操作裕度。根据 IEEE 802.3ck 规范对 112G 的规定,COM 裕度不得小于 3dB。

Cadence 112G SerDes PHY IP

为了补偿上述提及的无法避免的设计缺陷和挑战,IP 供应商为其 IP 设计了更高的裕度。Cadence 112G Extended Long-Reach(ELR)PHY IP 提供额外的性能裕度,通过反射消除和增强的 DSP 来应对设计缺陷。这些增强让我们为高损耗和高反射的通道提供更高的裕度。这些对生产系统行之有效的特性包括:

(文章来源公众号: Cadence楷登)

··································································································································································································································································

关于搏嵌电子

上海搏嵌电子技术有限公司(Shanghai BoardChain Electronics Technology Co., Ltd.),是一家专注于从事电子设计自动化(EDA)服务的高科技公司。

作为Cadence授权的渠道伙伴,搏嵌电子致力于服务客户的整个电子设计流程,在原理图和PCB设计、功能验证、模拟仿真等方面为客户提供高效的技术解决方案和专业的研发工具,加速客户的产品上市周期,提升客户产品的可靠性。搏嵌的核心团队10多年来,在消费电子、半导体、通讯、汽车电子、航空航天、物联网,工业控制、医疗器械、家电、5G产业链等众多领域服务了数千家客户。

欢迎关注“搏嵌电子”公众号

了解更多Cadence EDA技术分享