021-80120081

021-80120081免费服务热线

EDA领域需要运用许多不同的运算软件,然而EDA行业所面临的挑战在于,设计团队总需要采用当前的处理器来设计及创建下一代的SoC。

在1990年代和2000年代,微处理器公司将处理器的性能每年提高了约50%来解决这个问题。部分原因是摩尔定律在没有产生功耗问题的同时,提高了硅芯片的性能;还有部分原因来自于处理器架构的提升,可以通过更聪明的方法来执行乱序执行(Out-of-order Execution)、分支预测(Branch Prediction)以及解决所有其他设计上遭遇的困难。

摩尔定律提高了时钟(Clock Cycle)频率,而架构的改善也提高了每个时钟周期可执行的命令数(IPC)。因此,如果我们需要更高的性能,只需等待即可,当时的生活多美好!

然而两件事情的发生使生活不再那么美好:首先,由于功耗限制,不可能再增加微处理器的时钟频率;其次,改变架构也几乎变不出花样了。

从某种意义上说,摩尔定律还没有结束,在芯片上仍然可以放置越来越多的晶体管,但不再以增加的单执行线程(Single-Thread)性能来交付增加的处理器能力,而是以增加处理器核心数量来交付。

因此,不如我们使用“核心定律”(Core's Law)一词,即处理器核心的数量呈指数增长。但因为我们位在改变曲线的平坦处,所以这一名词并未引起关注,也从未流行。现在,处理器具有48核,甚至128核,这一点明显变成常态,而不太明显的议题则是,运算软件如何适应更多核。

秘密算法其实是一个大规模平行化的矩阵求解器。这是一种突破性算法,是Cadence在系统分析领域的秘密武器。它具有近乎线性的扩展度,而且不影响任何精准度。它运用大量低容量的机器,几乎具有无限的容量,却不需要真正具备任何大型计算机——一个在您需要时派不上用场,或者大多闲置、等待被使用的工具。整个基础架构可动态部署到云端(或数据中心)中,并具有容错重启功能——因为当大量的机器一起使用时,罕见的事也会发生。

许多EDA以稀疏矩阵(Sparse Matrices)形式编码来求解大量方程式。稀疏矩阵是其中大多数项目为零的矩阵。因为不需要显式记录为零矩阵项,这意味着它们可以非常有效地存储在电脑内存中。

通常,这些矩阵是对称的,由于只需要记录矩阵的一半,因此可以进一步节省成本。这是因为许多电气特性是对称的:从节点1到节点2的电容与从节点2到节点1的电容相同。

Cadence在过去几年中在计算软件(Somputational Software)方面取得的突破之一,就是强调如何在大量核心和/或服务器上使用这些大型稀疏矩阵进行矩阵代数运算,举例来说,Cadence的Voltus、Clarity、Celsius等都是相同的解决方案。

Sigrity X可提供仿真速度和设计处理量高达10倍的性能,而不会影响任何精准度。这是通过在云端(或大型本地数据中心)中进行大规模分布式仿真所实现。基本上与Clarity 3D Solver的基础相同,是以大规模分布式仿真技术,进行兼顾电源影响的信号完整性分析。分析信号完整性的最大挑战之一,就是受到影响的层面广大。功耗会影响温度,进而影响IR drop,再影响到时序,再影响到信号完整性。

混合求解器的另一个新发展是多线式检查。信号完整性探索与核心数量呈现线性关系(因为探索的每个配置完全独立,因此不需要连续通讯)。

Sigrity X技术可适用于Sigrity系列产品:PowerSI、PowerDC、XtractIM、SystemSI和OptimizePI。但是,以上并不是最新版Sigrity的唯一变革——Sigrity全新的用户界“Layout Workbench”非常易于使用。可根据您的喜好,变更成亮色或深色主题画面(正如同手机操作),也可取决于您所在的位置和一天中的时间做出调整——与Clarity 3D Solver所提供的GUI相同。

同时,Sigrity X还配备了最新的数据库,这使得在机器之间移动仿真文件变得更加容易,因为所有仿真类型的全部内容都封装在了单个文件中。保存功能也得到了改进,可以处理任何其他依赖的仿真数据(Dependencies)。

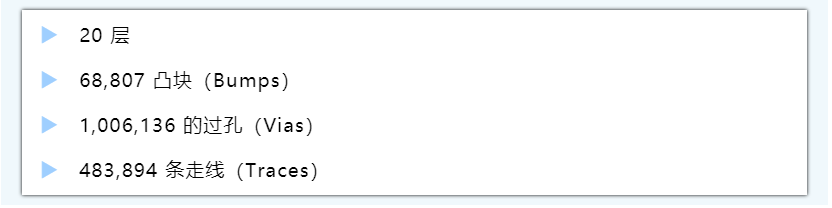

以下的范例说明了新版本性能的显著提升。该示例设计具有:

以上使用2019 PowerSI Hybrid Solver混合求解器,需要15天才能完成。而使用新的2021.1 Hybrid Solver混合求解器,并使用相同数量的核心,同样的过程只需1.5天即可完成。

当前,信号完整性分析的两个热门领域是PAM4和DDR5内存接口:

PAM4是一种使用四个电平、每个(恢复的)时钟周期传输两位的信号技术,它可应用于112G SerDes,以及即将到来的PCIe 6.0标准(尚未最终确定,但纳入PAM4则不会更改)。

DDR5是DDR DRAM接口的最新版本,正逐渐成为内存接口市场的流行领域。DDR5有望在2022年成为最常用的接口(Cadence与美光(Micron)已经持续在DDR5接口技术开发上合作多年)。

转载自Cadence楷登微信公众号

上海搏嵌电子技术有限公司(英文:Shanghai BoardChain Electronics Technology Co.,Ltd.)是Cadence官方授权代理商,在PCB设计、IC设计、封装设计、系统分析、模拟仿真等方面为客户提供高效的技术解决方案和专业的研发工具,欢迎致电咨询:400-0519-668。