021-80120081

021-80120081免费服务热线

Key Benefits

为了帮助您快速实现常规拓扑和标准接口,Cadence® Sigrity™ Advanced SI 技术能够以多种模式执行自动化的die-to-die信号完整性 (SI) 分析:

Advanced SI 技术采用频域、时域和统计分析方法,解决从DC到 56GHz (112Gbps) 以上的信号完整性问题。

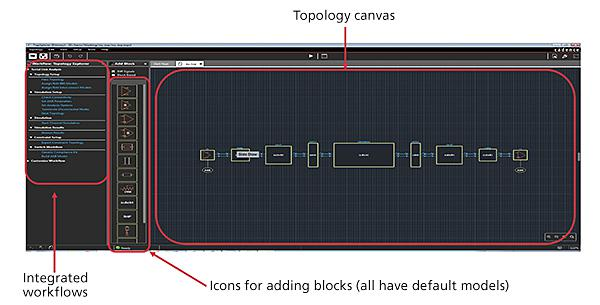

图 1:SystemSI 拓扑环境

Sigrity Topology Explorer

通用拓扑探索功能,是探索端到端的信号和电源拓扑的理想方案,包括用于同时执行 SI或瞬态电源完整性 (PI) 分析。此外,您还可以使用复杂的互连通道模型,并将它们连接到单个驱动器/接收器/离散元件,从而自动为互连模型上的每个端口复制电路。此功能包含在Sigrity Aurora软件中,其网络信息可直接从物理 PCB 或 IC 封装设计中自动提取。

Sigrity SystemSI 并行总线分析

端到端分析适用于如DDRx内存的源同步并行总线接口。包含过孔向导的前仿真功能使您可以快速生成并连接模型,并基于该模型展开后续设计。随着设计被优化完善,您可以更换更详细的模型,以反映实际的硬件设计。Advanced SI 包括以下功能:

并行仿真中考虑了介质损耗和导体损耗、反射、码间干扰 (ISI)、串扰和同步开关噪声 (SSN) 的影响。这些仿真可以充分考虑非理想电源分配系统的影响。图形化输出及后处理选项能为快速改进系统提供思路。

可以将仿真结果与常见 JEDEC 标准(例如 DDR4 和 DDR5)进行比较,以确保设计满足标准规范的要求。如有需要,可以配置额外测试以补充规范测试,或者针对专有 IP 创建自定义合规性测试包。

Sigrity SystemSI 串行链路分析

专注于高速 SerDes设计的chip-to-chip分析功能受到广泛业界认可,使用其基本模板可对诸如 PCI Express®(PCIe®)、HDMI、SFP+、XAUI、Infiniband、SAS、SATA 和 USB的设计进行早期评估。支持行业标准的 IBIS-AMI 发射器和接收器模型,即便串行链路含多个供应商生产的芯片,您也可以对其通道行为进行仿真。对于芯片模型开发人员,则可使用辅助开发IBIS-AMI 模型的技术。并且,可以添加含多个封装、连接器和电路板的模型,以反映整个通道。仿真将发现串扰问题,并验证芯片级“时钟和数据恢复”(CDR) 技术的有效性。全通道仿真(包括数百万个数据位)可确认整体误码率(BER),进而确定抖动和噪声水平是否在指定的公差范围内。您更可以借助于适用于常用高速接口(如 PCIe 5.0)的合规性测试包,来自动执行所需的信号质量检查;如果没有可用于首选标准的合规性测试包,您还可以进行自定义配置。

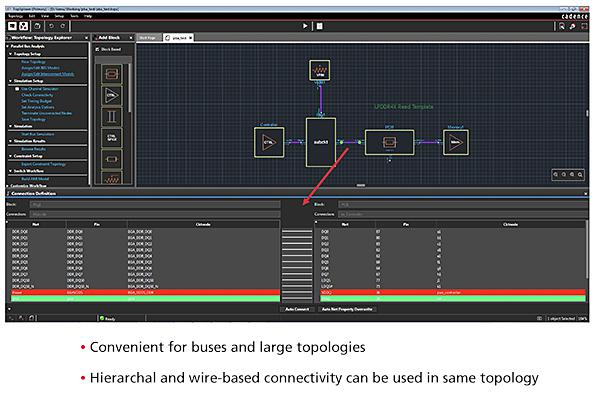

图 2:SystemSI直观的用户体验,便于用户轻松通过信号、电源和接地端口连接来连接耦合的互连模型

主要功能