021-80120081

021-80120081免费服务热线

Cadence 于 10 月 12 日发布了 Cadence Certus Closure Solution,这是同类型产品中首款采用大规模并行计算和分布式架构的全自动环境。Cadence Certus Closure Solution 环境实现了设计收敛的自动化,并将整个设计收敛周期从数周缩短至一夜之间 —— 包括从签核优化到布线、静态时序分析(STA)和参数提取。

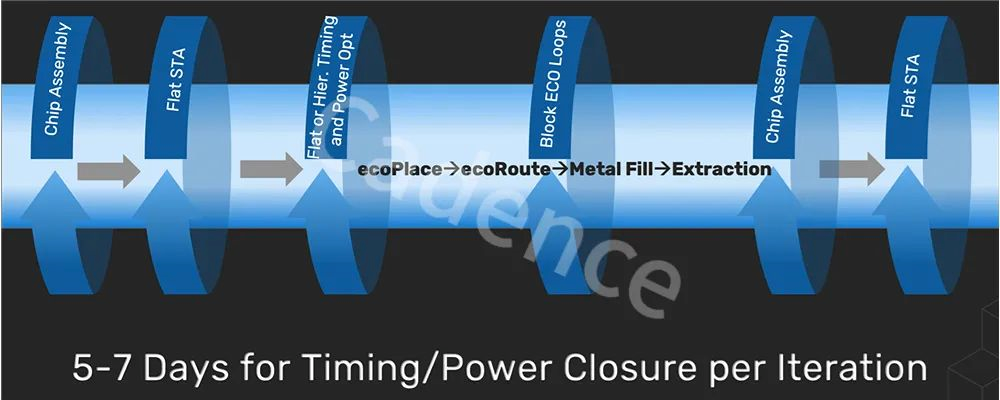

该解决方案支持无限容量,胜任大型芯片设计项目,与目前其他方法和流程相比,最多可将生产力提高 10 倍。传统流程如下图的蓝色轮轴所示,每个迭代单一阶段的完整运行都需要 5 - 7 天,且迭代次数无法提前预知,甚至最多需要 30 次。简单计算一下,全芯片所有流程加起来可能需要耗时 3 个月之久。

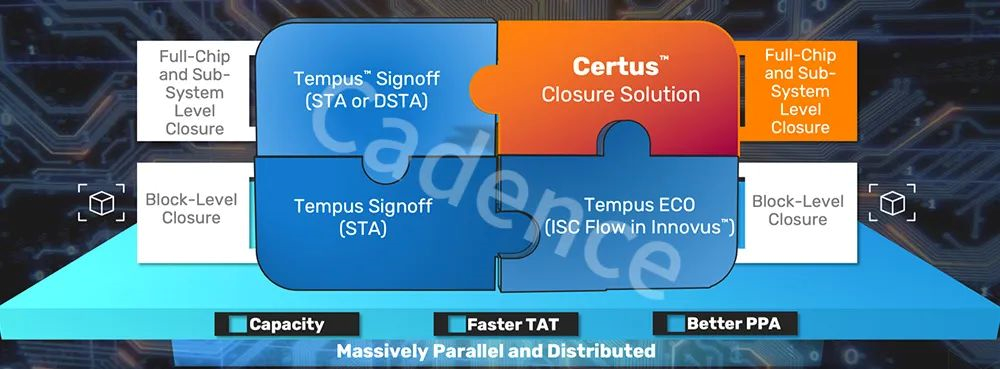

上述流程会用到两个主要工具,分别是用于模块层次优化的 Tempus ECO,以及用于 SoC 层面静态时序分析的 Tempus STA。这里缺失了全芯片(或子系统)优化与签核。至于分区间功耗恢复等则只能忽略,因为实在没时间处理。

Cadence Certus Closure Solution 将上述流程自动化,实现隔夜优化和签核收敛。在 Innovus 工作流程中,基于 Tempus 签核解决方案(STA 或 DSTA)及 Tempus ECO 的基础中,Certus Closure Solution 可以进一步发挥时序签核和 ECO 技术在广度和深度上的优势。

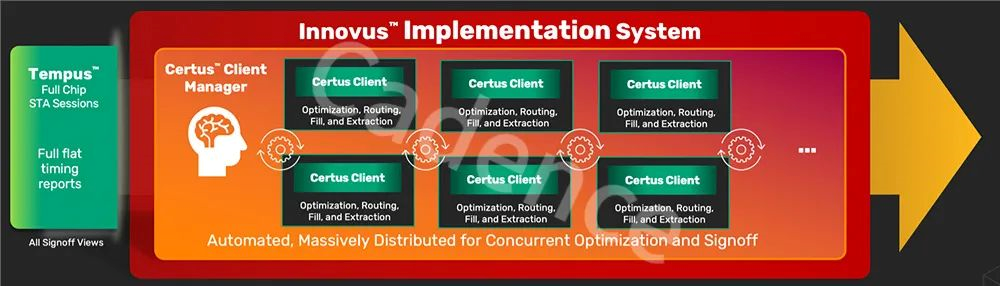

显而易见,我们是通过将所有任务大规模分布处理以及全流程自动化来达成这一目标的。下方图表列出了所有细节。作为大规模并行系统,管理器会负责控制所有任务,并将计算结果汇总以判定下一步该做什么。

此外,模块之间的功率恢复功能可以降低 10% - 15% 的功耗,全芯片最高降低 5%。这也就是文中之前提到的,人工流程的话根本没时间处理这个问题。

总结一下,Certus 的核心优势包括:

示例

我们来看几个例子。

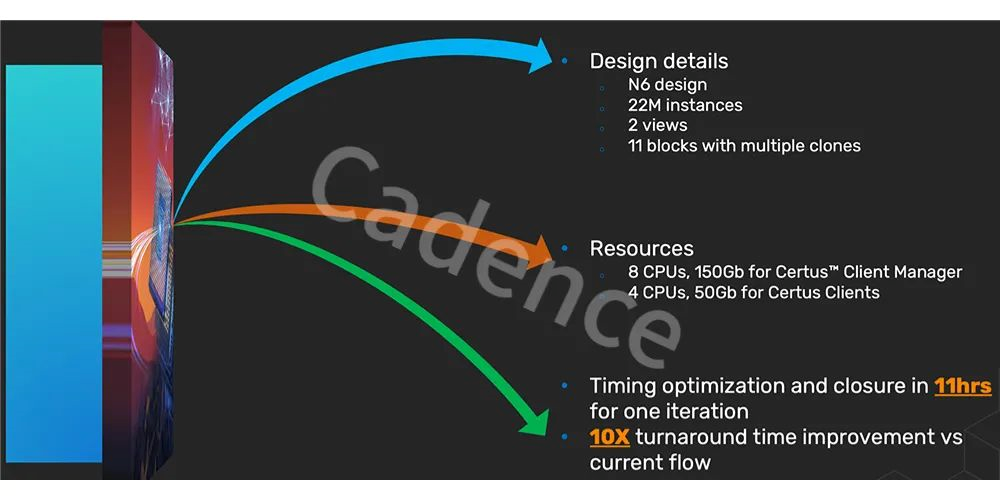

6nm,22M 逻辑单元,11 小时

(提升 10 倍)细节如上图

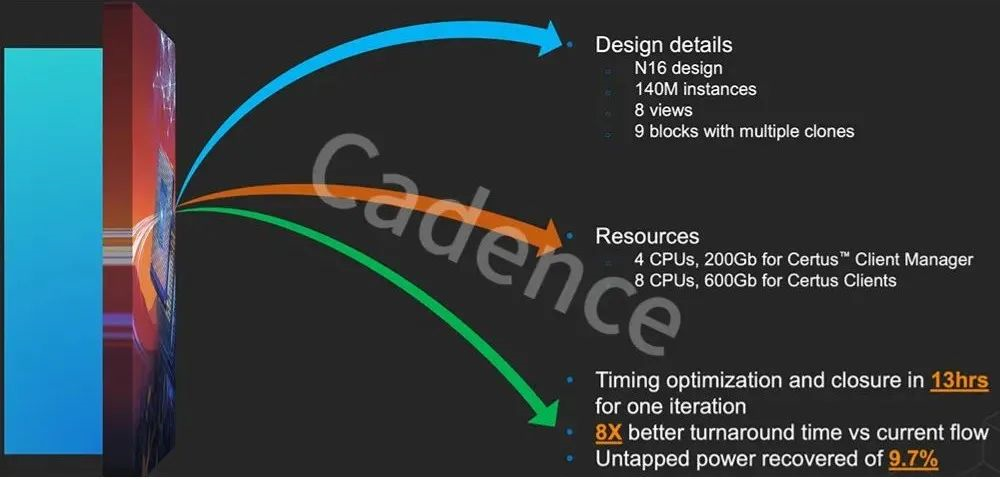

16nm,140M 逻辑单元,13 小时

(提升 8 倍)

(文章来源公众号: Cadence楷登)

··································································································································································································································································

关于搏嵌电子

上海搏嵌电子技术有限公司(Shanghai BoardChain Electronics Technology Co., Ltd.),是一家专注于从事电子设计自动化(EDA)服务的高科技公司。

作为Cadence授权的渠道伙伴,搏嵌电子致力于服务客户的整个电子设计流程,在原理图和PCB设计、功能验证、模拟仿真等方面为客户提供高效的技术解决方案和专业的研发工具,加速客户的产品上市周期,提升客户产品的可靠性。搏嵌的核心团队10多年来,在消费电子、半导体、通讯、汽车电子、航空航天、物联网,工业控制、医疗器械、家电、5G产业链等众多领域服务了数千家客户。

欢迎关注“搏嵌电子”公众号

了解更多Cadence EDA技术分享