021-80120081

021-80120081免费服务热线

12 月 26 日至 27 日,中国集成电路设计业 2022 年会暨厦门集成电路产业创新发展高峰论坛(ICCAD 2022)在厦门国际会展中心隆重召开,本次年会以“共创新发展,聚焦芯未来”为主题,深入探讨新形势下集成电路产业发展以及未来集成电路设计业面临的机遇和挑战。

在这场壬寅岁末的行业盛会上,Cadence(楷登电子)也带来了两场重量级演讲,集中分享了其对前沿趋势的洞察及业务布局。

26 日下午的高峰论坛上,Cadence 亚太及日本地区 IP 与生态系统销售群资深总监陈会馨发表了题为《但尽己力 成就未来》的主旨演讲。

演讲中,陈会馨首先向与会嘉宾分享了 Cadence 在 2022 年三个比较“特别”的动作:

陈会馨指出,受人工智能、大数据、5G、自动驾驶、物联网、生命科学等新兴技术对传统产业加速渗透改造的带动,全球半导体产业规模近年持续快速增长,EDA 市场也有望在 2020-2026 年实现体量翻番。

创新应用需求使芯片针对特定场景的优化愈发重要,系统产品本身的发展也正跨越硬件与软件、模拟与数字、电气与机械的边界,并向智能化的方向演进,由此驱动着系统公司越来越多开始设计自己的芯片,而半导体公司越来越需要提供完善的软件开发工具与接口,实现其最终产品的差异化。

基于对技术潮流的洞察,陈会馨表示 Cadence 已明确了数据分析、系统设计和芯片设计三大战略重点,将在数据中心、航太、自动驾驶、工业自动化等新兴产业做更多的战略部署。打造从 IP、芯片、PCB 到系统的端到端解决方案,以满足苛刻的设计要求并交付出色产品,在陈会馨看来,这一战略又可被分解为卓越设计、系统创新、普适智能三大支柱战略。

正如陈会馨所强调的,Cadence “首先还是一家 EDA 公司”,因此卓越设计正是旨在提供从 IP 组合到流片后确认(Validation)的完善设计工具及可扩展的云计算资源,帮助芯片设计团队开发面向特定应用场景的高性能计算核心,高效完成复杂 IC 设计中的功能划分(Partition)和布局布线综合优化,实现 IC/SoC 的上佳 PPA 表现,并能在这一过程中以更少的资源和更高的质量按时完成复杂 IC 设计项目。

系统创新,则是旨在扩展传统 EDA 功能,赋能完整电子系统设计与仿真优化,将信号完整性、电磁和电热分析从芯片和封装扩展到 PCB、模组乃至完整系统,并引入 FEM/CFD 等多物理场分析工具,在保障安全性的基础上实现系统软硬件协同优化,大幅精简执行系统分析、早期开发和安全验证的工作量和时间。陈会馨还特别提到,Cadence 在当下方兴未艾的 3D-IC 微系统领域,也已经推出一系列设计、仿真、签核工具。

普适智能,则是陈会馨认为三大战略中“最重要的一点”,在她看来,电子系统设计中智能技术的应用包括了设计流程和设计工具的智能化,除了将 AI/ML 技术引入传统电子设计工具、设计流程,Cadence 还可提供丰富的 NPU/DSP 等 IP 组合,赋能智能系统和功能的实现,设计团队可以通过创建专门的处理器来优化目标数据集算法,管理智能系统中固有的大规模并行和高吞吐量特性,为预期的工作负载设计高性能产品,并有效减少设计和实施所需的周期。

陈会馨还表示,在数据与算力需求爆发、芯片设计成本与复杂度抬升等因素影响下,计算软件正出现融合发展的趋势,凭借在计算软件方面积累的深厚专业知识,Cadence 在新的潮流中具有良好的竞争身位,并已经着力回应上述变化,提出了智能系统设计(Intelligent System Design)战略,陈会馨具体解读称,智能系统设计一方面将继续强化 Cadence 在 EDA/IP 领域优势地位,另一方面也会依托其计算软件质量、优化等方面核心能力向系统设计扩展,并积极推动 EDA 上云。

27 日上午的专题论坛上,Cadence 验证产品经理许克龙带来了题为《基于 FMEDA 的功能安全全流程解决方案》的技术分享。

许克龙表示,选择 FMEDA 这一主题,源于与客户交流中感受到的共性需求,随着车规芯片市场爆发,众多新团队纷纷开始布局车规芯片,工程师对功能安全的概念都非常清晰,但 ISO26262 标准与功能安全设计、验证实践之间还存在一定脱节。

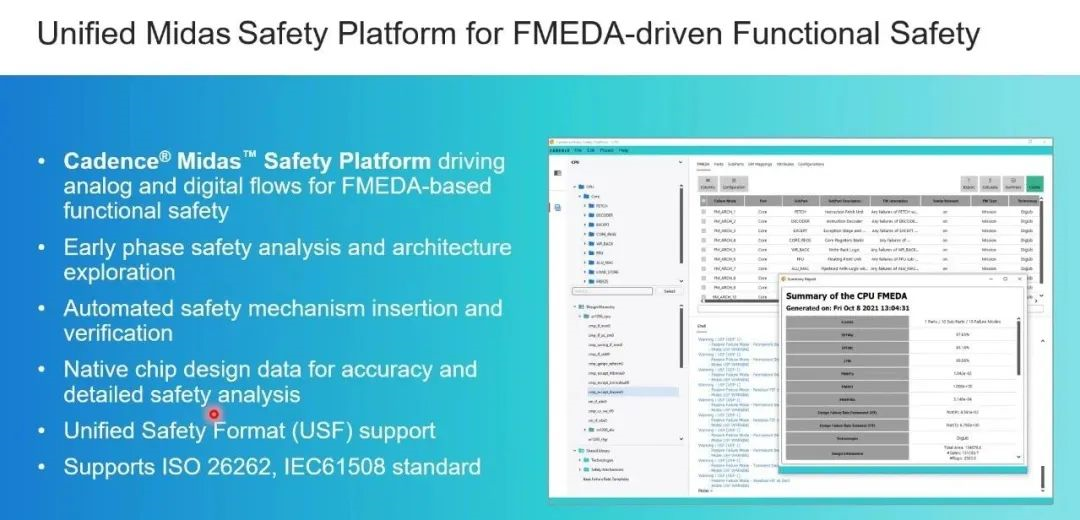

正是基于对行业痛点的洞察,Cadence 已推出 Midas 平台,由 FMEDA(失效模式影响和诊断分析)驱动整个 EDA 工具链,可望有效破解这一问题。

许克龙指出,车规芯片对质量、可靠性有极高要求,为了避免芯片硬件老化、随机错误乃至黑客攻击等导致的单点故障和系统失效,必须引入功能安全认证,在他看来,传统 FMEA(失效模式与影响分析)方法学主要聚焦于系统层面,而 FMEDA 则切入到了 SoC 和 RTL、门电路设计与功能验证层面。

根据许克龙介绍,Cadence 推出的 Midas 平台有这样几大特色:

在 Midas 平台,IC 设计团队可以调用丰富的 Cadence 设计、验证工具,如综合工具 Genus、实现工具 Innovus、一致性比对工具 Conformal 等。

随后,许克龙以一个简化的示例,具体展示了 Midas 平台由 FMEDA 驱动的分析流程,在定义项目所用器件、工艺后,Midas 平台可对基本失效率(BFR)进行预估,随后定义目标器件失效模式,在此基础上,具体的 IP 设计 RTL 可以通过简单的鼠标拖拽与 FMEDA 层次完成映射关联(Mapping),进行精准的故障仿真,仿真结果会以表格的形式呈现在图形界面中,能否“过标”一目了然,IP 功能安全数据通过自下而上合并,可进一步形成 SoC 级别结果。

许克龙还透露,Midas 平台可以在三个不同维度进行功能安全分析,首先是架构级,使用者可以通过预估的诊断覆盖率(DC)等关键参数,进行较高层次上概略的功能安全分析;而在 RTL 设计数据形成后,可以进行更为精细的安全分析;最终实际跑完故障仿真,可以得到高精度 DC 值等参数,进行精准的功能安全分析。

介绍中,许克龙还着重谈到了 Midas 平台的验证管理工具 vManager,功能安全仿真中,往往一个很小的模块在注入错误后也会产生成千上万个故障,因此需要功能强大的管理工具,vManager 除了能够管理海量注错数据,也会收集所有故障仿真之后的诊断覆盖率,提取关键数据进行整合并反标回 FMEDA,vManager 还支持原有功能仿真验证环境、脚本的复用,无需重新开发,对于 test case,vManager 也可以实现排序,根据效率高低进行优化和裁减,并自动调用 Cadence 各类验证引擎。

在介绍了 Midas 平台主要特性后,许克龙指出这一平台不仅支持数字和模拟 Full-flow,而且也是全自动调用,非常高效且兼具灵活性。除了数字功能安全验证之外,多样化的 IC 设计也可能涉及模拟和数字混合的场景,需要专门工具的辅助。在 Midas 平台都将不再是难题。

(文章来源公众号: Cadence楷登)