021-80120081

021-80120081免费服务热线

随着技术的发展,封装设计变得越来越复杂。新材料和制造工艺的出现,使得封装中可以有更多有源和无源元件。与此同时,信号完整性、电源完整性和热挑战也随之增加。以前可以在机械CAD工具中完成的简单设计,现在需要接受更为严格的设计规则检查。运行信号完整性(SI)分析和制造检查也势在必行。那么,如何顺利完成复杂封装设计的各个阶段呢?

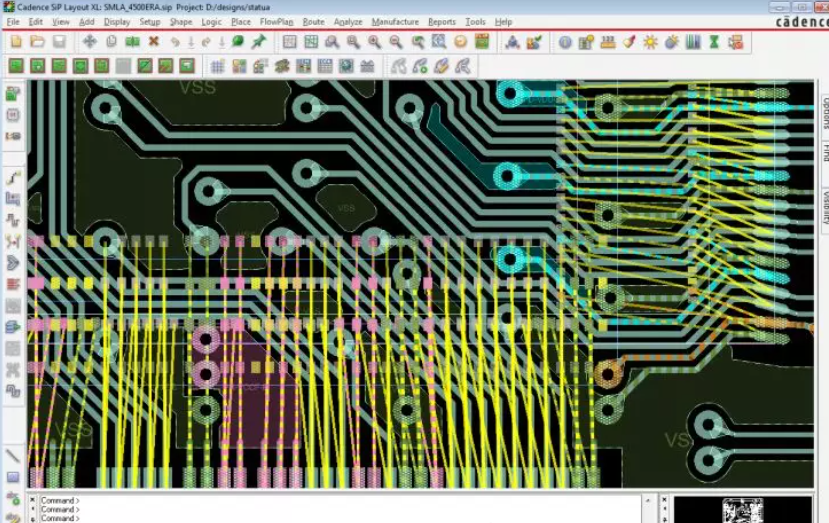

Allegro®SiP Layout工具,凭借大量命令和工具集可以帮助我们更快速地完成封装设计,并通过各级验证保障最终元件能在整个系统环境中完美运行。

从外部几何数据预置基板和元件

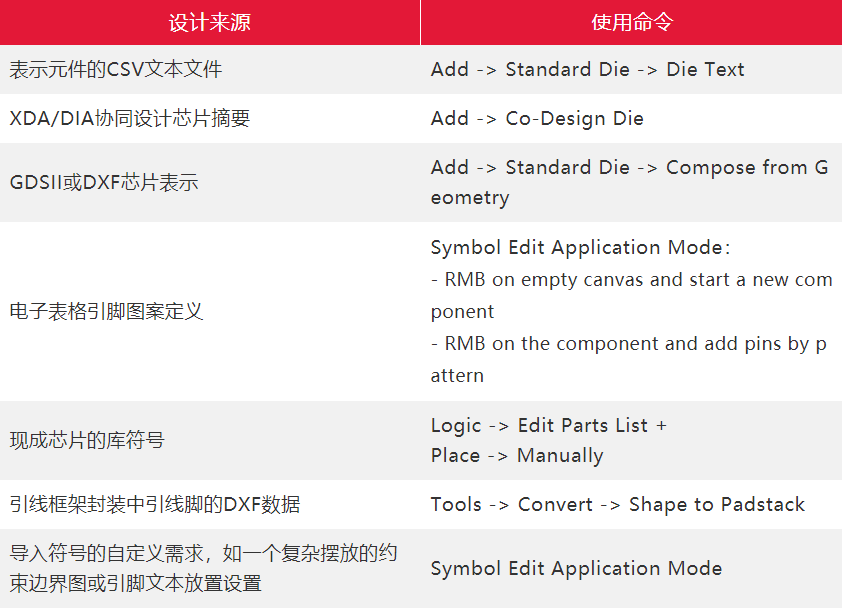

任何设计中,第一步都是准备好元件。如果我们有器件库和器件文件,便可以开始设计了。但是,如果我们只有一个芯片GDSII文件和简单的网络文本标签,或者芯片焊盘图案的电子表格引脚图,甚至只有一个来自基板供应商的定义的引脚图案、焊盘的DXF文件,要怎么办?

无论来源是芯片文本文件、协同设计芯片摘要还是制造几何数据,SiP Layout都能满足导入和转换需求。轻松几个命令便可以将数据转换为基板中完全定义的元件和符号;基板有网络指派,并做好了接合准备。此外,我们可以直接在SiP基板设计中完成这些工作,无需进入库元件或焊盘形状编辑器。因为在编辑器中,我们将失去整个封装的环境(重建智能基板期间的重要信息,包括几何数据)。

以下是一个简单的图表来了解选项细节:

更多的特定数据输入列表可通过点击:文件->导入和添加->标准芯片菜单项来查看,或咨询Cadence支持代表。

如果对于某个设置使用了不同数量存储器或不同电源的设计,我们有多种不同的选择并且想确保一次性输入所有数据,怎么做呢?不用担心,SiP Layout可以帮助我们发现各个不同的组合,并从主基板设计中提取单独的数据库用于验证、分析和制造。

2、将元件连接至封装引脚

我们将元件放置好并准备进行连接后,一切就变得简单了。但是,我们要确保在连接前完成阅读网表信息,从而确定要将哪个芯片焊盘连接到哪个封装的引脚上。

从电子表格、CSV文件、原理图或其他来源导入网络,或者根据引脚名称/编号以及芯片到封装引脚的优化分配即时定义网络。选择我们最容易获取的信息,这一步将显示芯片和引脚之间的连接线,此时我们便可以开始进行连线了。

3、执行物理/组件设计验证

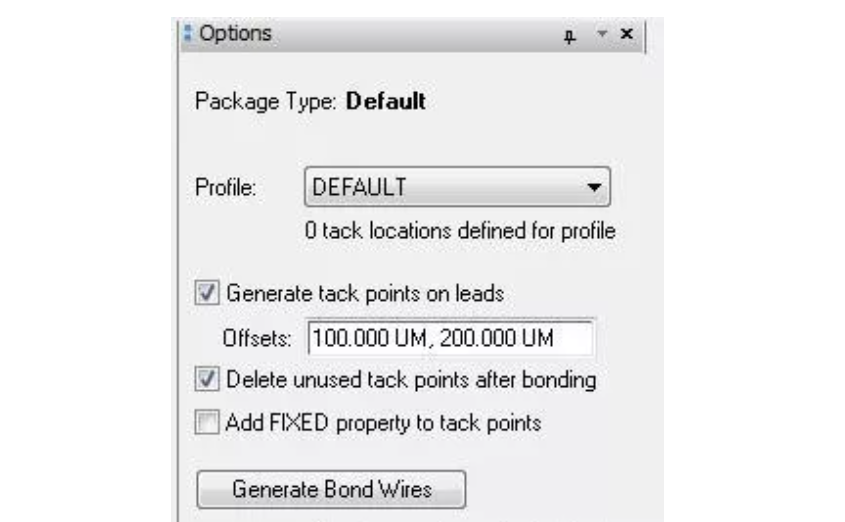

连线结束后,接下来应该验证设计的物理特性。现在开始对设计进行3D检查以确认设计情况(并且进行3D线至线DRC间距检查);点击View->3D Model,定义DRC需求,并生成视图。如果我们发现任何问题,可以直接在查看器中更改引脚剖面,重新运行DRC检查,并在情况完全符合我们要求时将新分布分配回layout数据库。

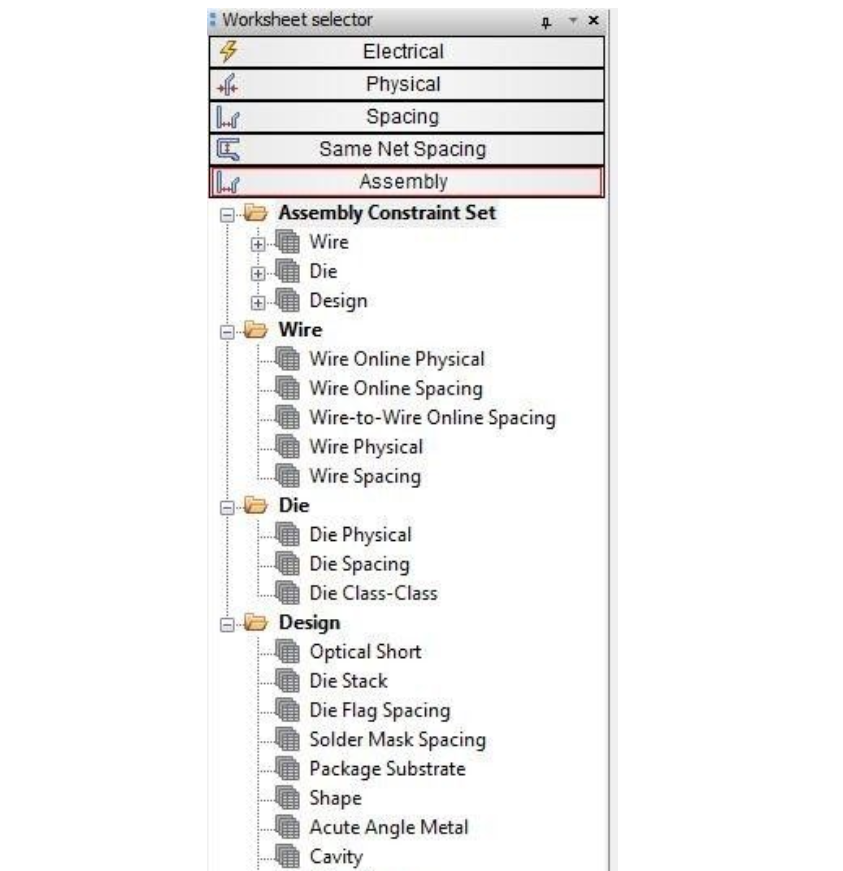

与3D检查同样重要的是,除了Constraint Manager电子表格中的标准物理、间距和电气规则之外,SiP Layout还提供了强大的装配规则检查。下图所示为装配规则检查类别:

如果我们的制造过程需要特定的专有规则,Cadence RAVEL option可以确定在设计上运行特定的规则检查。

4、电气特性分析

电气特性分析可以确保一切设计都在规格范围内。

Sigrity™XtractIM™工具是一个快速高性能的用于IC封装RLC检查和评估的工具。借助生成高精度宽带模型并支持复杂封装的功能,它适用于紧密集成的SiP Layout设计。Sigrity XtractIM工具无缝地从设计中提取所有细节——3D引线侧视线型、焊料凸块模型,甚至是开腔或者叠层芯片中芯片的位置和高度。

如果定义了多个设计变量,首先使用“Manufacture”菜单下的variant界面提取要分析的特定变量选项。如此一来,该工具便能了解到我们想要表征、检查和建模的设计选项。

5、生成制造数据和支持文档

在创建设计、添加逻辑、验证满足物理和间距要求、并确保信号、热和功率容差都符合规范之后,我们需要生成设计文档和制造数据。

无论我们的需求是否包括键合图、OLP数据、GDSII、DXF、Gerber或其他数据格式,基本上都可以在File->Export或Manufacture菜单下找到满足需求的导出转换器。

对于文件而言,无论我们需要设计的引脚连接报告、连通性报告,还是PDF文档,输出都轻而易举。如果我们需要突出显示设计的某些特定区域,使用3D查看器的标记和注释功能即可,截取带有文本符号的详细图像并纳入参考范围。

转载自Cadence楷登PCB及封装资源中心微信公众号

上海搏嵌电子技术有限公司(英文:Shanghai BoardChain Electronics Technology Co.,Ltd.)是Cadence官方授权代理商,在PCB设计、IC设计、封装设计、系统分析、模拟仿真等方面为客户提供高效的技术解决方案和专业的研发工具,欢迎致电咨询:400-0519-668。