021-80120081

021-80120081免费服务热线

2020年8月TSMC召开了技术研讨会与OIP生态系统论坛,Cadence公司在该系列活动中发布了一系列与TSMC相关的公告。Cadence公司数字与全定制/模拟流程均针对N3进行了完全优化和认证。

因此,Cadence工具支持所有可用于设计的TSMC工艺。尤其是N3、N4、N5、N6、N7、N16、N22、N28系列。当然,Cadence工具也支持更成熟的节点,比如N20和N10,但对于新设计来说,这两个节点并非最佳选择。

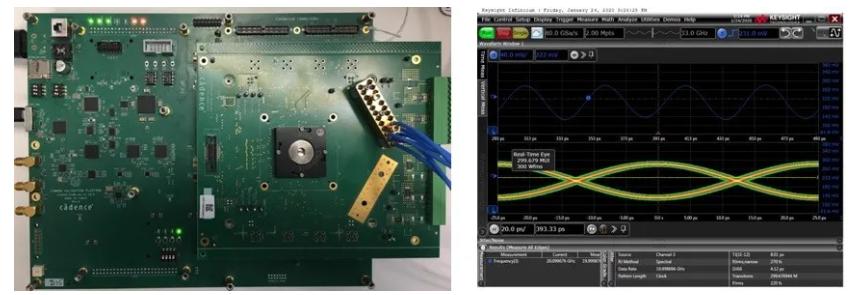

TSMC N7、N6和N5上的UltraLink D2D PHY IP

2019年11月,Cadence公司宣布推出Ultralink D2D PHY IP,详情参见《行业洞察I裸晶对裸晶互连:UltraLink D2D PHY IP》一文。当时是在N7工艺中进行设计应用。这次,我们在N6运行了芯片测试,并进行了全面的硅验证。我们还在N5上进行了流片,并等待从TSMC获取的相关结果。

媒体新闻稿中指出:

来自TSMC的带有完整硅特性数据的测试硅现已备齐,这是超高速、高级集成电路的一个重要里程碑。为了保证设计裕量、所有制程细节的性能、比特误码率(BER)、插入损耗和最大传输速度,广泛的硅验证是必要的。Cadence公司现已准备好通过其TSMC N7和N6制程中的UltraLink D2D PHY IP与客户沟通。Cadence公司最近还在TSMC N5技术中推出了UltraLink D2D IP,目前正在与早期采用的客户合作,预计今年晚些时候将测试硅的可用性。

最新技术:InFO和CoWoS

同时,使用了TSMC最新3DIC技术的Cadence流程也获得了认证,现在该技术已被分组进TSMC 3DFabric。

越来越多地,大量的设计规模化已采用“超越摩尔”的高级封装方法。对此,TSMC有两种主要方法,即InFO和CoWoS。InFO代表Integrated FanOut(集成FanOut),CoWoS代表Chip on Wafer on Substrate(基片上晶片的芯片)。这是两种采用系统级封装或3D集成电路技术的方法。在过去的一两年里,多晶粒封装已经成为最热门的设计领域之一。在2019年的HOT CHIPS大会上,许多高级设计都采用这种多晶粒封装方法。

而推动这一趋势的因素包括:

产量:巨大的晶粒产量不如同样数量的硅分裂成更小晶粒的产量

成本:只有系统的某些元件需要昂贵的先进制程

容量:这是系统获得足够存储的唯一方法

市场:这是一种使用相同硅来应对不同配置/市场的方式

从技术上讲,Cadence此次宣布的是:

“...TSMC最新的InFO和CoWoS multi-chip(let)封装解决方案、集成FanOut与RDL互连(InFO-R)和带有硅中介层(CoWoS-S)的芯片-晶片-基板的Cadence参考流程认证。”

详细描述为:

“借助Cadence Allegro®封装布局技术,最新的参考流程通过预防性和修正性的设计自动化,提供了更高效的设计规则检查签发/封装方法。

此外,通过Allegro Package Designer Plus中支持新的标准InFO技术文件和设计模块,结合Silicon Layout Option中新的设计规则检查验证和提高了50倍的高级除气de-gassing性能,客户可实现更优性能的InFO-R封装的布局自动化。

最后,Cadence Clarity™3D Solver已经通过了3D-EM提取认证,包括对CoWoS-S设计的S参数模型创建的新支持。"

转载自Cadence楷登PCB及封装资源中心微信公众号

上海搏嵌电子技术有限公司(英文:Shanghai BoardChain Electronics Technology Co.,Ltd.)是Cadence官方授权代理商,在PCB设计、IC设计、封装设计、系统分析、模拟仿真等方面为客户提供高效的技术解决方案和专业的研发工具,欢迎致电咨询:400-0519-668。