021-80120081

021-80120081免费服务热线

随着高速电路越来越普及,电路板设计密度越来越大,对于通讯行业、商用服务器、以及工控、军工领域对高速电路需求较多性能要求较高的地方,PCB的布线阻抗成为了一个必须关注的重要话题。我们知道在整个信号系统的传输链路里面,PCB板级的设计中会有较多的情况造成阻抗不连续或者突变。

比如布线线宽的改变、锐角走线、厚度的不一致、参考平面的改变不完整跨分割区域等。那么这些阻抗不连续或者改变会对传输的信号质量造成较大的影响。Cadence Allegro 17.4布线阻抗分析可以让工程师直观的分析出阻抗的具体情况,能够评估每根走线上的阻抗变化,对工程师衡量信号的质量起着关键性的作用。

使用Cadence Allegro 17.4软件进行布线阻抗分析的具体方法

1、选取一个XC6SLX25的电路板的实例文件,如下图所示,选取的这个文件,截图的部分是DDR3的内存颗粒芯片部分,假设需要分析DDR3走线的阻抗。

2、选取电路板8层的叠层情况如下,从下图中我们可以看出,这是一个8层电路板,实例的电路比较特殊,其实是一个软硬结合的电路板。

3、在叠层管理器的右侧点击Signal Integrity折叠按钮,可以展开信号完整性的计算表格,在这个表格里面可以对布线中所涉及到的单线阻抗和查分阻抗进行预计算。比如下图中,当在TOP,BOOTOM层布线0.1mm的单线的时候,布线所具有的阻抗特性是50.676欧姆。若布线差分线的时候0.1mm的线宽和0.160的间距,布线所具有的阻抗特性是90.898欧姆。

4、接下来我们通过阻抗分析工具来分析DDR3部分的具体阻抗控制情况,选择Analyze–Impedance Workflow启动分析工具。

5、在Impedance Workflow流程中,选择Net Based模式,点击Select Nets弹出网络选择框。在选择框中选择我们需要分析的网络。假设需要分析的是DDR3的数据线,点击选择好相应的DDR3数据线FBA_D<0>到FBA_D<64>共计64个数据网络后,点击Apply按钮进行确认,然后点击OK退出。

6、点击Start Analysis按钮就可以开始对选择的网络进行阻抗分析。

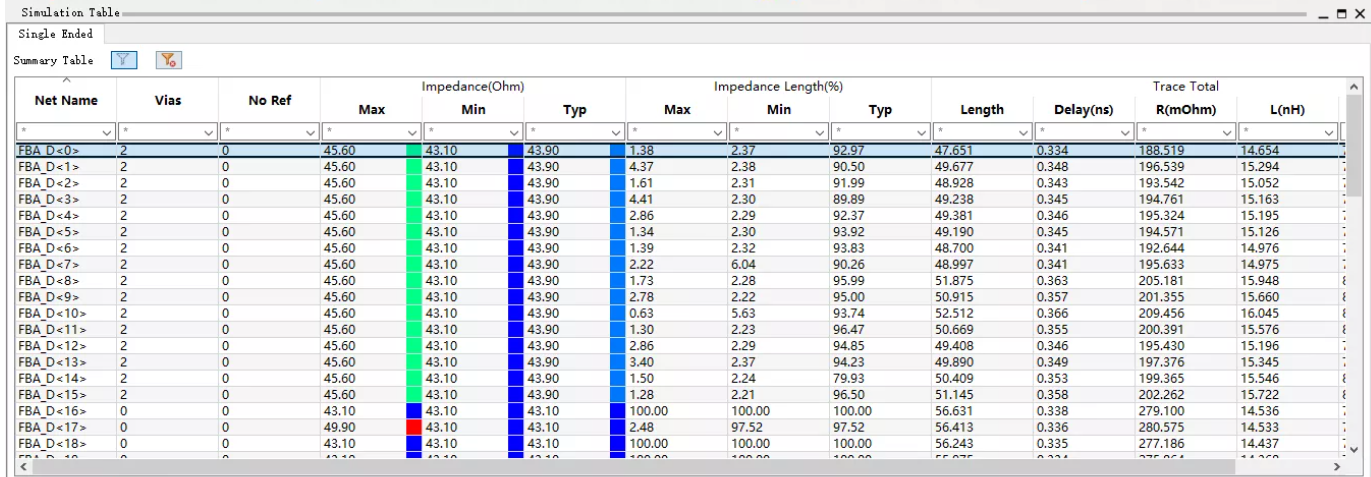

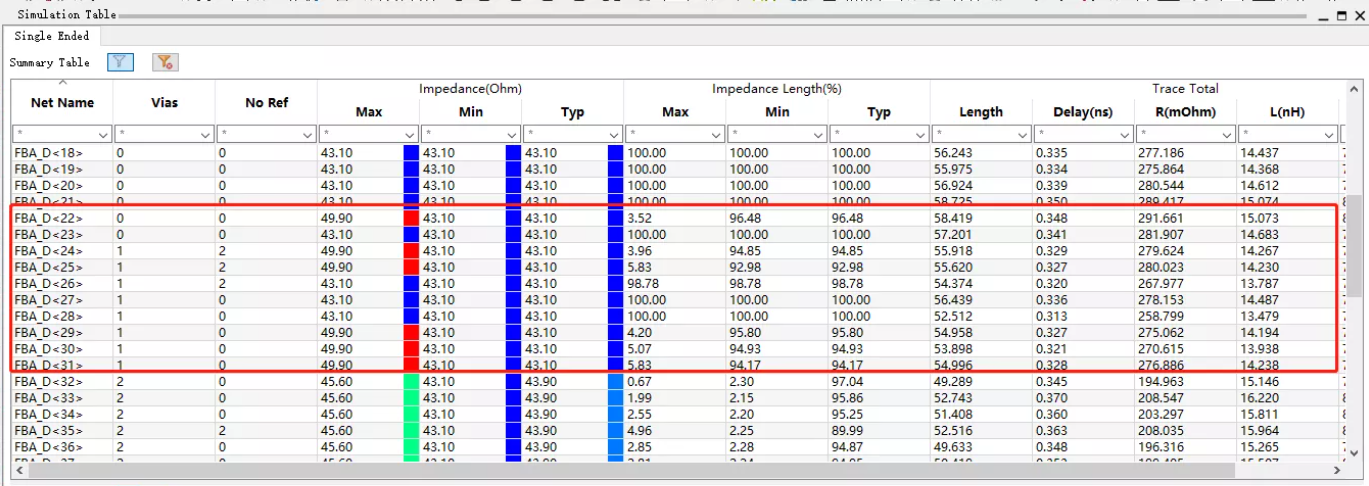

7、等待分析的进度条完成以后,就可以查看分析完成的结果。分析的结果有两种显示方式,一种是表格的方式显示出来,一种是色度图表的方式显示出来。选择Impedance Table按钮可以开启分析结果的表格显示方式。

8、如下图在分析的结果中,你们可以明显的看到FBA_D<22>,FBA_D<24>,FBA_D<29>,FBA_D<30>这些数据线存在阻抗突变的问题,MAX栏目给出最大的阻抗数据是100欧姆。点击上面表格中的具体的网络,下面表格中可以给出具体网络特征情况,包括阻抗线长比例、网络NET长度、延迟时间、RLC参数等。这些分析能够让我们发现设计中存在的问题。

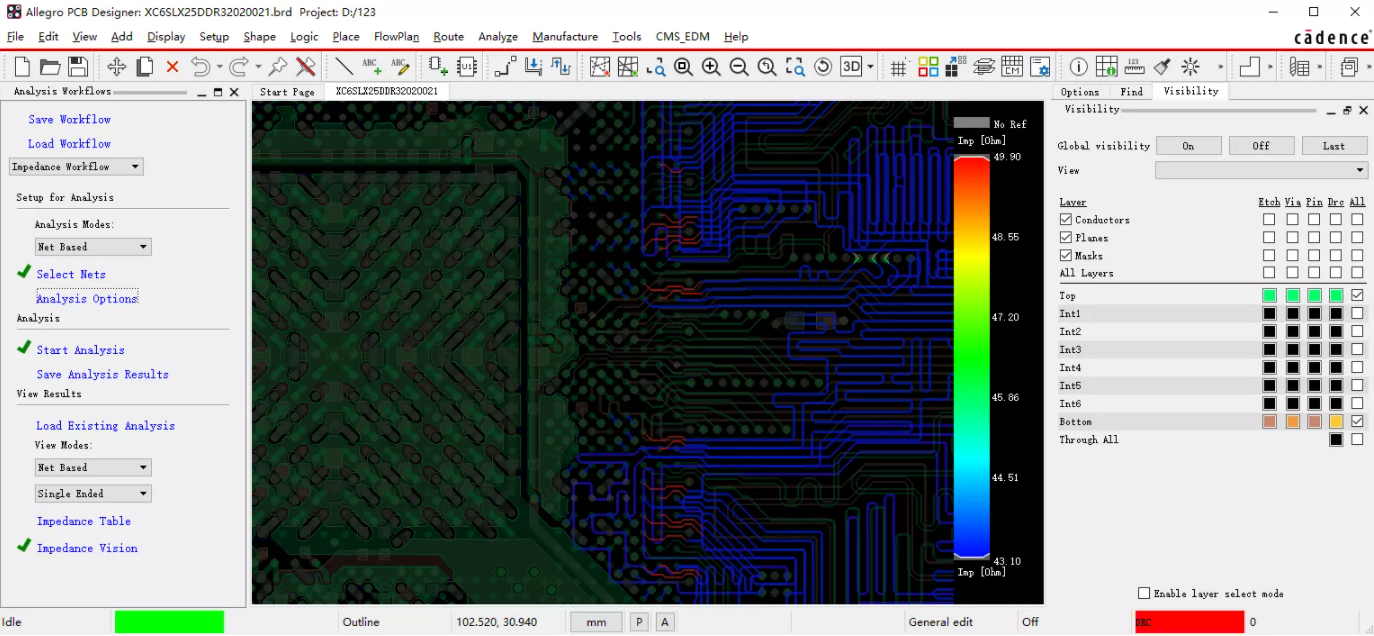

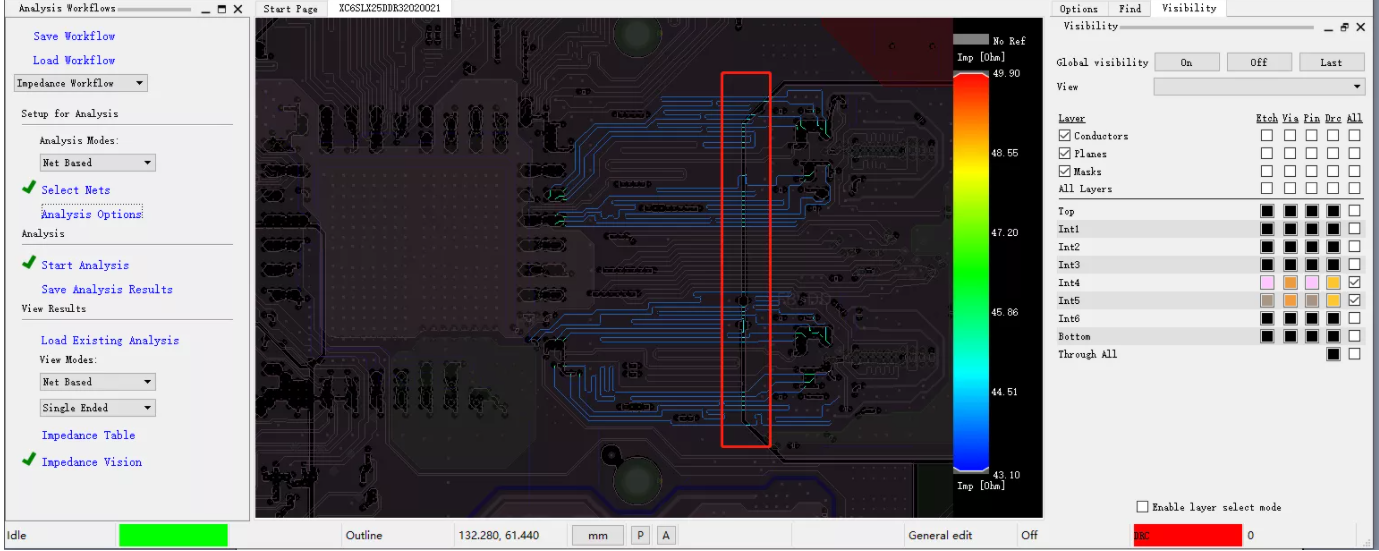

9、点击Impedance Vision按钮分析的结果可以用色度图表的方式显示出来,色图卡通过颜色的不同,标识出了每个布线阻抗变化的情况,这个显示方式相对比较直观些,更容易让工程师发现问题。

10、放大分析可以看到FBA_D<29>,FBA_D<30>等几个网络,布线是在INT6层,因为相邻的GND层铜皮被切割后参考平面不完整造成的跨分割,导致了阻抗变大。

通过上面的学习让我们看到了Cadence Allegro 17.4为PCB阻抗分析的方法,既然通过分析知道了阻抗不连续原因,就可以通过修补铜皮完善平面的方法来解决这个阻抗突变的问题。这个例子可以让工程师通过布线阻抗分析功能,随时了解PCB布线上阻抗的具体情况,随时修改,衡量信号完整性以及提升设计的准确性,为高速PCB阻抗控制提供了一种更加便捷高效途径。