021-80120081

021-80120081免费服务热线

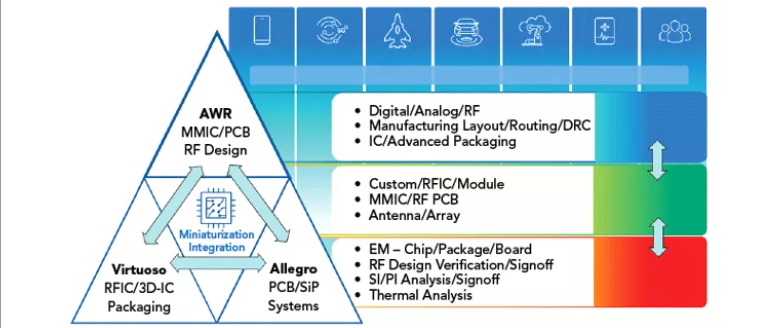

5G无线系统和连接设备正在每一个可以想象的行业中激增,促使技术领先者利用市场机会,开发由性能、尺寸和成本决定和区分的射频产品。传统上,利用最新先进技术节点的定制或专有集成电路(IC)设计一直是实现差异化的途径,但今天的复杂设计正在超越只考虑芯片内部设计的界限。

射频和混合信号设计工作不仅包括多样化的半导体工艺,还包括先进的跨层封装和系统级封装(SiP)和封装中的封装(PiP)技术,以及使用先进互连技术实现的3D-IC。成功的产品需要在开发的整个设计、分析和签收阶段,在系统层面上考虑可能影响最终产品整体性能的每一个可能的组件之间的相互影响。所有影响结果的电气因素——微观和宏观的——都必须考虑。

为了在竞争激烈的5G无线市场中获胜,公司需要电子设计自动化(EDA)解决方案实现从芯片到系统的完整和全面的射频工作流程。为了实现这一目标,工程团队需要融合EDA平台以及仿真和分析技术,以确保宝贵的工程时间用于设计,而不是将数据从一个工具转移和翻译到另一个工具。EDA软件开发商必须提供一个高效的前端到后端的互操作工作流程,以最大限度地提高用户的生产力。

随着Cadence在2020年从美国国家仪器公司收购了AWR®,Cadence®AWR Design Environment®平台的最新V16版本提供了完整和全面的RF工作流程。

01、异构技术

异构集成减轻了同构系统芯片(SoC)解决方案的高成本压力,使设计者能够在使用较新的封装技术的基片上结合成熟的RFIC和MMIC设计。先进的集成方法,如扇出式晶圆级封装(fan-out wafer-level packaging),可以产生更小、更有效的系统,然而这些高度集成的系统更加复杂,容易因各个组件的相互依赖性、复杂的跨结构互连网络以及从多个来源汇集跨平台设计数据的挑战而产生错误。平台的互操作性对于跨芯片、封装和电路板设计的多技术集成至关重要。

新发布的AWR Design Environment V16版本通过工作流程自动化使周转时间减少至少50%。它通过利用射频知识产权(IP)创建和跨平台仿真,包括IC和封装(Virtuoso工具流程)和电路板(Allegro工具流程)来实现这一目标。此外,Clarity™3D Solver和Celsius®Thermal Solver的集成和互操作性提供了电热协同仿真和如射频前端这样的大规模高密设计的耦合分析。V16版本实现的射频工作流程创新始于在不同的加工领域对应的设计平台间设计数据和软件IP的共享和传输方式的基础性进步。在Cadence旗下,V16软件所引入的射频集成水平显著提高了工程团队的生产力。

Cadence的工具平台不断发展,以解决所支持的工艺技术的制造、设计和分析要求。其设计流程自动化可管理极其复杂的芯片、封装和电路板系统的开发。由于系统级集成要求跨这些不同的技术进行射频设计,在开始设计之前,工程师要从多个来源获取信息:业务需求、可靠性约束、制造工艺和供应链数据。对于企业和大型设计团队来说,需要有效地共享库,使用公司授权和预先批准的部件和叠层材料进行工作,这增加了将产品快速推向市场的挑战。为了共享设计数据、利用不同工具的独特功能、减少或消除系统集成瓶颈,平台之间的互操作性是必要的。射频设计和加工版图设计团队之间的任何脱节都会消耗工程资源并直接影响开发进度。

想象一下,在AWR软件中创建的射频IP可以无缝地集成到用较新的工艺技术和集成方法设计的系统中。开发团队现在有一个高效的射频工作流程,使他们能够提取AWR射频IP/设计数据,并在适当的RFIC、PCB或SiP平台上重复使用。AWR V16版本引入对Cadence统一库和技术文件的支持,建立了AWR、Virtuoso和Allegro平台之间的互操作性。

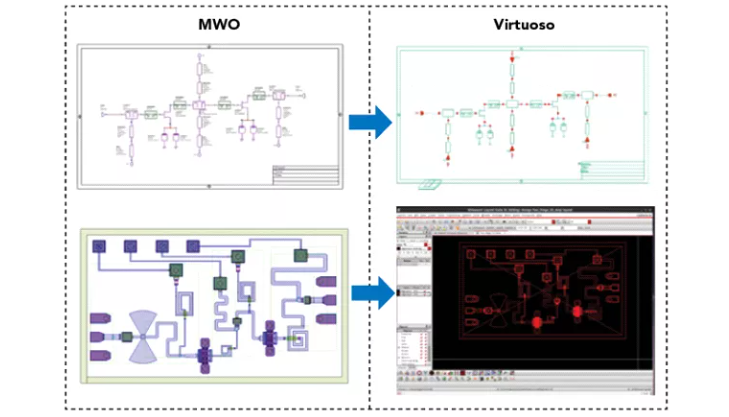

02、Virtuoso和AWR工作流程

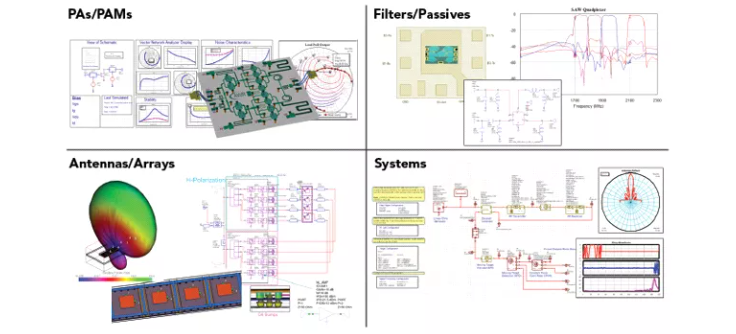

利用Cadence EDA解决方案的共享架构和数据,AWR V16版本提供了新的射频工作流程,从Microwave Office软件中获取完整的设计,并将原理图和版图设计传递给Virtuoso和/或Allegro平台。这些数据在一个统一的库中,包含了电路设计的所有构建块。这使设计团队能够操作Allegro SiP或Virtuoso SiP双向实现流程和Virtuoso RF Solution物理实现流程作为主要版图设计工具,其射频IP原理图和版图设计数据由V16软件提供。Virtuoso RF Solution流程可捕获Microwave Office RF IP,使设计人员能够在单一环境中展示、整合和验证MMIC和嵌入式RF封装设计。共享数据库通过简化设计流程,轻松可靠地访问Microwave Office内开发的RF IP,实现了更实用的封装和IC协同设计。

例如,Microwave Office用户可以通过电路设计、优化和电磁验证来设计片外无源元件,然后决定最佳的实现技术。在某些情况下,最好的无源元件网络可能需要跨越IC和封装的边界来实现。对于射频模块来说通常是这样,理想的滤波器设计、匹配网络和功率放大器输出级的负载终端同时使用了芯片和封装基板上的元件。

在Virtuoso射频解决方案环境中,Spectre®仿真平台引擎可以仿真Microwave Office线性模型,支持带有嵌入式Microwave Office IP的IC和模块协同设计。将该IP导入Virtuoso流程的能力延伸至MMIC设计。由于大多数MMIC模型和PCell库是由III-V代工厂作为工艺设计套件(PDK)定义和实现的,Microwave Office MMIC设计流程会在设计中使用该PDK的目标半导体工艺。由此产生的MMIC原理图和布局可以作为一个统一的库设计导出,并导入Virtuoso环境。

03、ALLEGRO和AWR工作流程

从IC到电路板,一个RF设计的PCB工作流程开始于从Allegro部件和电路板定义创建统一的库和技术文件(technical files)。AWR V16软件中新的统一库导入向导读取通用库和技术文件中的Allegro符号(symbols)和引脚图(footprints),并将这些数据转换为AWR PDK,可用于使用标准设计输入和仿真方法创建射频设计。完成设计后,射频工程师使用AWR V16软件中的一个新工具,将子电路的原理图和版图设计包括所有底层层次导出到统一库设计中。

在后端,版图设计工程师需要访问根据公司批准的材料清单(BOM)和目标制造工艺设计的完整数据。基于Allegro源自组织批准的BOM和工艺技术的部件,射频工程和布局团队能提高设计移交的效率和可靠性,同时减少射频设计和制造要求之间的差异导致的来回协调。

04、多物理场

历史上,大型射频结构,如相控阵馈电网络,一直被手动分割成较小的结构,使用最大和性能最强的计算资源进行分析。AWR V16版本集成了用于设计关键互连、RFIC、MMIC、模块、PCB和SoC设计的Clarity 3D Solver 3D电磁仿真器,通过利用Cadence的分布式并行处理技术,克服了传统电磁分析软件的限制,该技术以10倍的速度提供了几乎无限的容量。Clarity 3D求解器为射频设计者提供了随时获得高容量电磁分析的机会,用于大型复杂射频/混合信号系统的设计验证和签核,得到了超越AWR AXIEM 3D平面和AWR Analyst 3D有限元方法(FEM)求解器所提供的处理能力。

Clarity与Microwave Office平台的整合是一个自动化过程,整个仿真设置操作完全在AWR环境中进行。一旦仿真完成,一个包含输入几何结构、仿真设置和S参数结果的数据集就会自动组装起来,并与给定的电磁文件相关联,用于绘图、测量和随后的提取、电路仿真、调整和优化。该链接除了支持S参数外,还支持网格剖分结果、电流分布和电磁场分布可视化数据,使设计人员能够使用AWR Design Environment平台中已有的丰富的三维电磁结果显示。

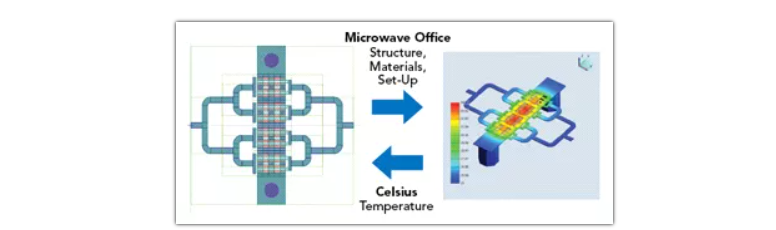

05、热分析

芯片电路和电子系统公司,特别是那些使用集成电路封装和/或多技术模块的公司,面临着可能破坏项目进度的芯片散热挑战。AWR软件中的Cadence Celsius热解器为射频器件、PCB和模块设计提供了一个解决方案,支持使用来自AWR Microwave Office软件的模型信息进行电热分析,使用现有的MMIC设计数据和几何形状,如版图设计、材料属性和来自射频仿真的功耗值。解算器在IC版图的相关分辨率下提供完整的IC温度分布结果,可作为图形化的3D温度叠加,以及返标温度回网表用于电路仿真。

热分析提供了关于工作温度可能降低射频性能和威胁器件可靠性的洞察力。通过在Celsius Thermal Solver中直接使用从Microwave Office软件中获得的模型和功耗信息,设计人员可以实现更准确的分析结果。额外的对象如散热器等也可以添加进来,和芯片一起作为一个新的结构导出,用于热分析,这使设计者能够研究散热器策略,得到最好的散热方案。

随着射频系统的激增和采用异构技术集成以在更小的空间内实现更大的功能,设计平台和多技术工作流程必须具有互操作性。AWR Design Environment V16平台包含了创新的功能,通过在Virtuoso和Allegro设计平台内对AWR平台射频/微波设计IP的无缝跨平台和多物理学集成,以及通过Clarity和Celsius求解器对完整的大规模设计进行电磁和热分析,提高工程生产力。

从芯片到系统,工程师可以在Cadence提供的全面的从前到后的射频工作流程中更好地解决跨结构、多技术的产品开发挑战。AWR V16正在进一步简化产品开发、提高用户生产力,消除设计人员在孤岛式工具之间切换的非生产性时间和交互周期所带来的低效率和洞察力损失。

转载自Cadence楷登微信公众号

上海搏嵌电子技术有限公司(英文:Shanghai BoardChain Electronics Technology Co.,Ltd.)是Cadence官方授权代理商,在PCB设计、IC设计、封装设计、系统分析、模拟仿真等方面为客户提供高效的技术解决方案和专业的研发工具,欢迎致电咨询:400-0519-668。